如何实现PCIe Gen3/Gen4接收端链路均衡测试?

时间:2020-04-06 阅读:2971

这是关于如何实现PCIe Gen3/Gen4接收端链路均衡测试的系列介绍,小泰将分别从理论篇到实践篇,为您讲述PCIe 3.0/4.0的链路均衡的工作原理及对链路均衡的测试和调试。

本期为理论篇,主要介绍PCIe 3.0&4.0的链路均衡,包括:

1)发送端的均衡: FFE

2)接收端的均衡: CTLE和DFE

3)链路均衡过程

PCIe接口自从被推出以来,已经成为了PC和Server上重要的接口。为了更高了数据吞吐率,PCI-SIG组织于2010年推出了PCIe 3.0,数据速率达到了8GT/s;于2017年推出了PCIe 4.0,数据速率达到了16GT/s。PCIe 3.0已经是PC上的标配接口;而PCIe 4.0目前仍处于Server上,在PC上也在开始普及。

*,PCIe 1.0和2.0使用的是普通的FR4板材和廉价的接插件。为了实现在这样的物理介质上进行有效的信号传输,PCI-SIG组织使用了8b/10b编码和发送端的去加重技术,来保证信号质量:

在PCIe 1.0中,去加重值为固定值3.5dB;

在PCI 2.0中,去加重值为3.5dB或6.0dB中的任何一个,也是为固定值,无法动态调整。

但是随着速率的翻倍,为了在PCIe 3.0和4.0中仍然使用普通的FR4板材以及廉价的接插件。

PCI-SIG组织对规范做了两方面的改进:

使用128b/130b编码来代替8b/10b编码,使得编码效率大幅提高;

使用动态均衡技术,来代替先前代的静态均衡技术;

通过这两方面的改进,PCI-SIG组织实现了在速率翻倍的同时,仍能保持使用普通的FR4板材和廉价接插件。本应用笔记就聚焦于PCIe 3.0和4.0中的动态均衡技术,介绍其原理、实现及其相关的一致性测试。这样一种动态均衡技术,在spec中被称作“Link Equalization”(链路均衡,简称为LEQ)。

▼ ▼ ▼

本系列包含理论篇和实践篇两个部分

理论篇主要介绍PCIe 3.0/4.0的链路均衡的工作原理。实践篇则侧重于对链路均衡的测试和调试。

PCIe 3.0&4.0的链路均衡

在PCIe 3.0和4.0中的链路均衡技术相较于先前代要复杂得多,这样一种动态均衡技术可以分为两个方面进行讨论:

均衡特性方面:从这个方面来说,相对于先前代的均衡来说,3.0和4.0中的均衡技术的硬件性能指标要求更高了。在本应用笔记中,2.1节和2.2节讨论它的技术细节。

协议方面:为了实现动态地调整均衡设置,需要协议层的配合,这是通过PHY层的LTSSM状态机中的Recovery.Equalization子状态来实现的。在本应用笔记中,2.3节讨论它的技术细节。

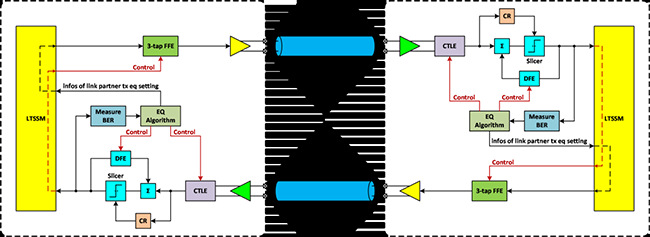

我们先来从均衡特性的角度来看看PCIe 3.0和4.0的均衡,如下图1展示了在PCIe 3.0/4.0中所使用的全部均衡技术,在Tx端有FFE(Feed Forward Equalizer,前馈均衡器);在Rx端有:CTLE(Continuous Time Linear Equalizer,连续时间线性均衡器)和DFE(Decision Feedback Equalizer,判决反馈均衡器)。

图1. LEQ硬件实现的模块框图

通过FFE和CTLE,可以去除大部分由ISI所引入的抖动;通过DFE可以进一步去除ISI,它还能去除部分的阻抗失配所造成的反射。通过这些均衡处理,就能够保证在接收端判决输入处将眼图打开。

除了上述这些均衡特性上的支持外,在协议层(LTSSM)中还规定需要通过协议的方式来动态调整链路上的均衡设定值,这整个过程称作链路均衡(Link Equalization,LEQ)。

在链路均衡过程中:

本地端按照某个初始Tx EQ的设定来发送数据;

对端在接收到数据时,会根据误码率或信号质量来判断该Tx EQ是否合适;

若不合适,对端会通过协议向本地端请求一个新的Tx EQ值;

本地端在接收到这个请求值之后,会改变Tx EQ的值。

通过这一动态过程,就能够保证链路上的Tx EQ为优值。与此同时,本地端和对端也会同时调整Rx EQ。通过动态地调整Tx EQ和Rx EQ,就能够灵活地适应不同的信道情况。