FESTO/德国费斯托 品牌

代理商厂商性质

上海市所在地

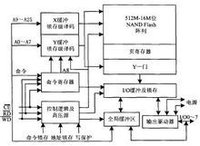

缓冲寄存器又称缓冲器,它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。由于缓冲器接在数据总线上,故必须具有三态输出功能。

1、电信设备。在数据传输中,用来弥补不同数据处理速率速度差距的存储装置叫做缓冲器。把数据存放到缓冲器中的技术叫做缓冲。

2、生化术语。缓冲液:化学试剂。用于缓冲PH的变化,常用于生物工程实验,如DNA、RNA等物质的提取和提纯,酶的性质的测定,蛋白质的分离等等。缓冲:某些试剂具有使溶液在加入酸或碱性物质的时候PH变化不明显的作用,这种作用叫做缓冲。

主要用来完成介质液体或气体波动压力趋向于平稳的容器。

接口集成电路语

zui基本线路构成的门电路存在着抗干扰性能差和不对称等缺点。为了克服这些缺点,可以在输出或输入端附加反相器作为缓冲级;也可以输出或输入端同时都加反相器作为缓冲级。这样组成的门电路称为带缓冲缓冲寄存器器的门电路。

带缓冲输出的门电路输出端都是1个反相器,输出驱动能力仅由该输出级的管子特性决定,与各输入端所处逻辑状态无关。而不带缓冲器的门电路其输出驱动能力与输入状态有关。另一方面。带缓冲器的门电路的转移特性至少是由3级转移特性相乘的结果,因此转换区域窄,形状接近理想矩形,并且不随输入使用端数的情况而变化、加缓冲器的门电路,抗干扰性能提高10%电源电压。此外,带缓冲器的门电路还有输出波形对称、交流电压增益大、带宽窄、输入电容比较小等优点。不过,由于附加了缓冲级,也带来了一些缺点。例如传输延迟时间加大,因此,带缓冲器的门电路适宜用在高速电路系统中。

在CPU的设计中,一般输出线的直流负载能力可以驱动一个TTL负载,而在连接中,CPU的一根地址线或数据线,可能连接多个存储器芯片,但存储器芯片都为MOS电路,主要是电容负载,直流负载远小于TTL负载。故小型系统中,CPU可与存储器直接相连,在大型系统中就需要加缓冲器。

任何程序或数据要为CPU所使用,必须先放到主存储器(内存)中,即CPU只与主存交换数据,所以主存的速度在很大程度上决定了系统的运行速度。程序在运行期间,在一个较短的时间间隔内,由程序产生的地址往往集中在存储器的一个很小范围的地址空间内。指令地址本来就是连续分布的,再加上循环程序段和子程序段要多次重复执行,因此对这些地址中的内容的访问就自然的具有时间集中分布的倾向。数据分 基本原理布的集中倾向不如程序这么明显,但对数组的存储和访问以及工作单元的选择可以使存储器地址相对地集中。这种对局部范围的存储器地址频繁访问,而对此范围外的地址访问甚少的现象被称为程序访问的局部化(Locality of Reference)性质。由此性质可知,在这个局部范围内被访问的信息集合随时间的变化是很缓慢的,如果把在一段时间内一定地址范围被频繁访问的信息集合成批地从主存中读到一个能高速存取的小容量存储器中存放起来,供程序在这段时间内随时采用而减少或不再去访问速度较慢的主存,就可以加快程序的运行速度。这个介于CPU和主存之间的高速小容量存储器就称之为高速缓冲存储器,简称Cache。不难看出,程序访问的局部化性质是Cache得以实现的原理基础。同理,构造磁盘高速缓冲存储器(简称磁盘Cache),也将提高系统的整体运行速度CPU一般设有一级缓存(L1 Cache)和二级缓存(L2 Cache)。一级缓存是由CPU制造商直接做在CPU内部的,其速度极快,但容量较小,一般只有十几K。PⅡ以前的PC一般都是将二级缓存做在主板上,并且可以人为升级,其容量从256KB到1MB不等,而PⅡ CPU则采用了全新的封装方式,把CPU内核与二级缓存一起封装在一只金属盒内,并且不可以升级。二级缓存一般比一级缓存大一个数量级以上,另外,在CPU中,已经出现了带有三级缓存的情况。

基本原理布的集中倾向不如程序这么明显,但对数组的存储和访问以及工作单元的选择可以使存储器地址相对地集中。这种对局部范围的存储器地址频繁访问,而对此范围外的地址访问甚少的现象被称为程序访问的局部化(Locality of Reference)性质。由此性质可知,在这个局部范围内被访问的信息集合随时间的变化是很缓慢的,如果把在一段时间内一定地址范围被频繁访问的信息集合成批地从主存中读到一个能高速存取的小容量存储器中存放起来,供程序在这段时间内随时采用而减少或不再去访问速度较慢的主存,就可以加快程序的运行速度。这个介于CPU和主存之间的高速小容量存储器就称之为高速缓冲存储器,简称Cache。不难看出,程序访问的局部化性质是Cache得以实现的原理基础。同理,构造磁盘高速缓冲存储器(简称磁盘Cache),也将提高系统的整体运行速度CPU一般设有一级缓存(L1 Cache)和二级缓存(L2 Cache)。一级缓存是由CPU制造商直接做在CPU内部的,其速度极快,但容量较小,一般只有十几K。PⅡ以前的PC一般都是将二级缓存做在主板上,并且可以人为升级,其容量从256KB到1MB不等,而PⅡ CPU则采用了全新的封装方式,把CPU内核与二级缓存一起封装在一只金属盒内,并且不可以升级。二级缓存一般比一级缓存大一个数量级以上,另外,在CPU中,已经出现了带有三级缓存的情况。

高速缓冲存储器,即Cache。我们知道,数据分布的集中倾向不如程序这么明显,如果把在一段时间内一定地址范围被频繁访问的信息集合成批地从主的系统中,CPU访问数据时,在Cache中能直接找到的概率,它是Cache的一个重要指标,与Cache的大小、替换算法、程序特性等因素有关。增加Cache后,CPU访问主存的速度是可以预算的,64KB的Cache可以缓冲4MB的主存,且都在90%以上。以主频为100MHz的CPU(时钟周期约为10ns)、20ns的Cache、70ns的RAM、为90%计算,CPU访问主存的周期为:有Cache时,20×0.9+70×0.1=34ns;无Cache时,70×1=70ns。由此可见,加了Cache后,CPU访问主存的速度大大提高了,但有一点需注意,加Cache只是加快了CPU访问主存的速度,而CPU访问主存只是计算机整个操作的一部分,所以增加Cache对系统整体速度只能提高10~20%左右。

德国*费斯托缓冲器 DYEF/DYSC常见型号:

DYEF-M4-Y1

DYEF-M4-Y1F

DYEF-M5-Y1

DYEF-M5-Y1F

DYEF-M6-Y1

DYEF-M6-Y1F

DYEF-M8-Y1

DYEF-M8-Y1F

DYEF-M10-Y1

DYEF-M10-Y1F

DYEF-M12-Y1

DYEF-M12-Y1F

DYEF-M14-Y1

DYEF-M14-Y1F

DYEF-M16-Y1

DYEF-M16-Y1F

DYEF-M22-Y1F

DYEF-S-M4-Y1

DYEF-S-M5-Y1

DYEF-S-M6-Y1

DYEF-M6-Y1F

DYEF-M8-Y1

DYEF-M8-Y1F

DYEF-M10-Y1

DYEF-M10-Y1F

DYEF-M12-Y1

DYEF-M12-Y1F

DYEF-M14-Y1

DYEF-M14-Y1F

DYEF-M16-Y1

DYEF-M16-Y1F

DYEF-M22-Y1F

DYSC-4-4-Y1F

DYSC-5-5-Y1F

DYSC-7-5-Y1F

DYSC-8-8-Y1F

DYSC-12-12-Y1F

DYSC-16-18-Y1F

DYSC-20-18-Y1F

DYSC-25-25-Y1F

DYSC-X3

负责人:龙伟

公司:上海维特锐实业发展有限公司

地址:上海市普陀区中江路889号曹杨商务大厦 1501-1502

: