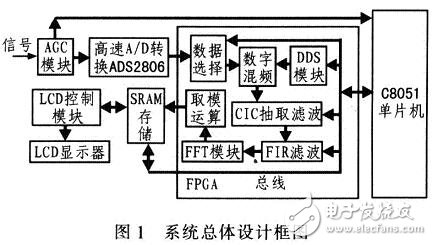

设计方案

图1为系统设计总体框图。该系统采用C8051($8.5125)系列单片机中的 C8051($8.5125)F121作为控制器,CvcloneⅢ系列EP3C40F484C8($86.5000)型FPGA为数字信号算法处理单元。系统设计遵循抽样定理,在时域内截取一段适当长度信号,对其信号抽样量化,按照具体的步骤求取信号的频谱,并在LCD上显示信号的频谱,同时提供友好的人机会话功能。该系统zui小分辨率为1 Hz,可分析带宽为0~5 MHz的各种信号。

由于单片机C8051($8.5125) F121内部集成A/D转换器,能够有效测量自动增益控制AGC压差,计算出对输入信号的放大倍数;另外,该单片机内置高速控制内核和丰富的存储器,使其能够控制整个系统;EP3C40F484C8($86.5000)型FPGA内置丰富的存储器资源,确保该系统具有足够的空间存储采集的点数,完成离散傅里叶变换、数字滤波器、数字混频等信号处理。

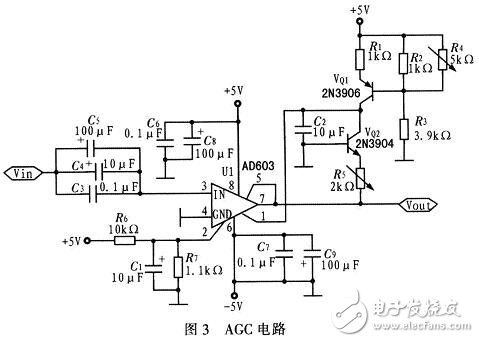

AGC电路

输入信号经高速A/D采样,信号幅度必须满足A/D的采样范围,zui高为2-3V,因此该系统设计应加AGC电路。AGC电路采用AD603($6.4440)型线性增益放大器。图3为AGC电路。

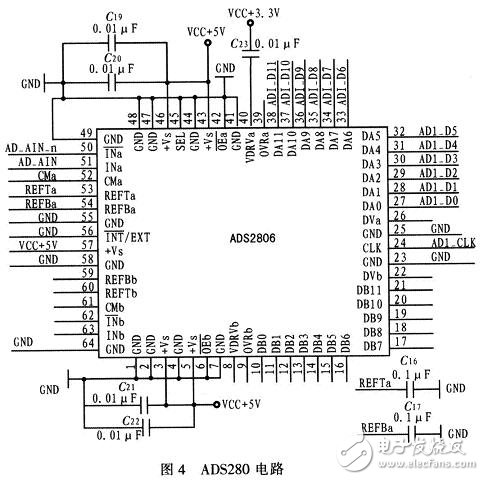

A/D转换电路

ADS2806($21.5437)是一款12位A/D转换器,其特点为:无杂散信号动态范围(SFDR)为73 dB;信噪比(SNR)为66 dB;具有内部和外部参考时钟;采样速率为32 MS/s。图4为ADS2806($21.5437)的电路。为使A/D转换更稳定,在A/D转换器的电源引脚上增加滤波电容,抑制电源噪声。该电路结构简单,在时钟CLK的驱动下,数据端口实时输出数据,供FPGA读取。

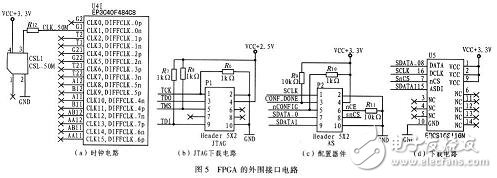

FPGA及外围接口模块

选用Cyclone($898.9000)Ⅲ系列 EP3C40F484($86.5000)型FPGA,该器件内部有39 600个LE资源,有1 134 000 bit的存储器,同时还有126个乘法器和4个PLL锁相环。由于该器件内部有大量资源,因而可满足其内部实现数字混频、数字滤波、以及FFT运算。FP -GA正常工作时,主要需要的外部接口有:时钟电路、JTAG下载电路、配置器件及下载电路。图5为FPGA的外围接口电路。

该系统能够方便地在LCD上显示信号的频谱结构图。操作简单,非常适合教学实验室学生使用。

文章来源:电子发烧友